# CHERIOT Architecture specification Version 0.6 (draft)

Saar Amar, Tony Chen, David Chisnall, Felix Domke, Nathaniel Wesley Filardo, Kunyan Liu, Robert M. Norton, Yucong Tao, Robert N. M. Watson, Hongyan Xia

26th July 2024

## **Abstract**

Small embedded cores have little area to spare for security features and yet must often run code written in unsafe languages and, increasingly, are exposed to the hostile Internet. CHERIOT (Capability Hardware Extension to RISC-V for Internet of Things) builds on top of CHERI and RISC-V to provide an ISA and software model that lets software depend on object-granularity spatial memory safety, deterministic use-after-free protection, and lightweight compartmentalization exposed directly to the C/C++ language model. This can run existing embedded software components on a clean-slate RTOS that scales up to large numbers of isolated (yet securely communicating) compartments, even on systems with under 256 KiB of SRAM.

## Acknowledgments

This document contains some elements from the CHERI ISA Specification<sup>1</sup>, which is licensed under the Creative Commons Attribution 4.0 International License. To view a copy of this license, visit:

http://creativecommons.org/licenses/by/4.0/

We acknowledge all the authors of that report:

| Robert N. M. Watson      | Peter G. Neumann      | Jonathan Woodruff   | Michael Roe       |

|--------------------------|-----------------------|---------------------|-------------------|

| Hesham Almatary          | Jonathan Anderson     | John Baldwin        | Graeme Barnes     |

| David Chisnall           | Jessica Clarke        | <b>Brooks Davis</b> | Lee Eisen         |

| Nathaniel Wesley Filardo | Richard Grisenthwaite | Alexandre Joannou   | Ben Laurie        |

| A. Theodore Markettos    | Simon W. Moore        | Steven J. Murdoch   | Kyndylan Nienhuis |

| Robert Norton            | Alexander Richardson  | Peter Rugg          | Peter Sewell      |

| Stacey Son               | Hongyan Xia           |                     |                   |

as well as the many other contributors to the CHERI project:

| Sam Ainsworth      | Ross J. Anderson  | Ruben Ayrapetyan    | Hadrien Barral        |

|--------------------|-------------------|---------------------|-----------------------|

| Thomas Bauereiss   | Stuart Biles      | Andrew Bivin        | Peter Blandford-Baker |

| Matthias Boettcher | David Brazdil     | Reuben Broadfoot    | Kevin Brodsky         |

| Ruslan Bukin       | Brian Campbell    | Gregory Chadwick    | Serban Constantinescu |

| Chris Dalton       | Nirav Dave        | Dominique Devriese  | Mike Dodson           |

| Lawrence Esswood   | Jonas Fiala       | Wedson Filho        | Anthony Fox           |

| Paul J. Fox        | Franz Fuchs       | Ivan Gomes Ribeiro  | Paul Gotch            |

| Tom Grocutt        | Khilan Gudka      | Brett Gutstein      | Jong Hun Han          |

| Andy Hopper        | Alex Horsman      | Timothy Jones       | Asif Khan             |

| Myron King         | Joe Kiniry        | Chris Kitching      | Wojciech Koszek       |

| Robert Kovacsics   | Karthik Muthusamy | Patrick Lincoln     | Marno van der Maas    |

| Anil Madhavapeddy  | Ilias Marinos     | Tim Marsland        | Ed Maste              |

| Alfredo Mazzinghi  | Kayvan Memarian   | Dejan Milojicic     | Andrew W. Moore       |

| Will Morland       | Alan Mujumdar     | Prashanth Mundkur   | Edward Napierala      |

| Philip Paeps       | Lucian Paul-Trifu | Austin Roach        | Colin Rothwell        |

| John Rushby        | Hassen Saidi      | Hans Petter Selasky | Andrew Scull          |

| Muhammad Shahbaz   | Bradley Smith     | Lee Smith           | Ian Stark             |

| Ramy Tadros        | Andrew Turner     | Richard Uhler       | Munraj Vadera         |

| Jacques Vidrine    | Hugo Vincent      | Philip Withnall     | Bjoern A. Zeeb        |

|                    |                   |                     |                       |

Ihttps://github.com/CTSRD-CHERI/cheri-specification

# The CHERI-RISC-V pseudocode is derived from the Sail CHERI-RISC-V model<sup>2</sup>, which has the following license:

This CHERI Sail RISC-V architecture model here, comprising all files and directories except for the snapshots of the Lem and Sail libraries in the prover\_snapshots directory (which include copies of their licenses), is subject to the BSD two-clause licence below.

Copyright (c) 2017-2021 Alasdair Armstrong, Thomas Bauereiss, Brian Campbell, Jessica Clarke, Nathaniel Wesley Filardo (contributions prior to July 2020, thereafter Microsoft), Alexandre Joannou, Microsoft, Prashanth Mundkur, Robert Norton-Wright (contributions prior to March 2020, thereafter Microsoft), Alexander Richardson, Peter Rugg, Peter Sewell

All rights reserved.

This software was developed by SRI International and the University of Cambridge Computer Laboratory (Department of Computer Science and Technology) under DARPA/AFRL contract FA8650-18-C-7809 ("CIFV"), and under DARPA contract HR0011-18-C-0016 ("ECATS") as part of the DARPA SSITH research programme.

This software was developed within the Rigorous Engineering of Mainstream Systems (REMS) project, partly funded by EPSRC grant EP/K008528/1, at the Universities of Cambridge and Edinburgh.

This project has received funding from the European Research Council (ERC) under the European Union's Horizon 2020 research and innovation programme (grant agreement 789108, ELVER).

Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

- Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

- Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

THIS SOFTWARE IS PROVIDED BY THE AUTHOR AND CONTRIBUTORS ''AS IS'' AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE AUTHOR OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

<sup>2</sup>https://github.com/CTSRD-CHERI/sail-cheri-riscv

# The RISC-V pseudocode is derived from the Sail RISC-V model<sup>3</sup>, which has the following license:

This Sail RISC-V architecture model, comprising all files and directories except for the snapshots of the Lem and Sail libraries in the prover\_snapshots directory (which include copies of their licences), is subject to the BSD two-clause licence below.

Copyright (c) 2017-2021 Prashanth Mundkur, Rishiyur S. Nikhil and Bluespec, Inc., Jon French, Brian Campbell, Robert Norton-Wright, Alasdair Armstrong, Thomas Bauereiss, Shaked Flur, Christopher Pulte, Peter Sewell, Alexander Richardson, Hesham Almatary, Jessica Clarke, Microsoft, for contributions by Robert Norton-Wright and Nathaniel Wesley Filardo, Peter Rugg, Aril Computer Corp., for contributions by Scott Johnson

All rights reserved.

This software was developed by the above within the Rigorous Engineering of Mainstream Systems (REMS) project, partly funded by EPSRC grant EP/K008528/1, at the Universities of Cambridge and Edinburgh.

This software was developed by SRI International and the University of Cambridge Computer Laboratory (Department of Computer Science and Technology) under DARPA/AFRL contract FA8650-18-C-7809 ("CIFV"), and under DARPA contract HR0011-18-C-0016 ("ECATS") as part of the DARPA SSITH research programme.

This project has received funding from the European Research Council (ERC) under the European Union's Horizon 2020 research and innovation programme (grant agreement 789108, ELVER).

Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

- Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

- Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

THIS SOFTWARE IS PROVIDED BY THE AUTHOR AND CONTRIBUTORS ''AS IS'' AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE AUTHOR OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

<sup>3</sup>https://github.com/riscv/sail-riscv

# **Contents**

| I | Sof  | ftware model and toolchain                                | 13 |

|---|------|-----------------------------------------------------------|----|

| 1 | Intr | roduction                                                 | 15 |

|   | 1.1  | The CHERIOT RTOS Model                                    | 16 |

|   | 1.2  | Security goals                                            | 17 |

|   |      | 1.2.1 Heap memory safety                                  | 17 |

|   |      | 1.2.2 Local stack memory safety                           | 18 |

|   |      | 1.2.3 Cross-compartment stack memory safety               | 18 |

|   |      | 1.2.4 Global memory safety                                | 19 |

|   |      | 1.2.5 Higher-level security properties                    | 19 |

|   |      | 1.2.6 Threat model                                        | 19 |

| 2 | Con  | npartment model                                           | 21 |

|   | 2.1  | Compartments define spatial ownership                     | 22 |

|   | 2.2  | Threads define temporal ownership                         | 23 |

|   | 2.3  | Execution at the intersection of threads and compartments | 24 |

|   | 2.4  | Compartment switches enforce compartment isolation        | 24 |

|   | 2.5  | Context switches enforce thread isolation                 | 25 |

|   | 2.6  | Adding shared libraries                                   | 26 |

| 3 | RTO  | OS implementation                                         | 29 |

|   | 3.1  | Per-thread state                                          | 30 |

|   | 3.2  | The loader                                                | 30 |

|   | 3.3  | Interrupt handling                                        | 31 |

|   | 3.4  | Synchronization and scheduling primitives                 | 31 |

|   | 3.5  | The memory allocator                                      | 32 |

|   | 3.6  | Error handling                                            | 32 |

|   | 3.7  | Other components                                          | 32 |

| 4  | C/C- | ++ language and toolchain extensions        | 35 |

|----|------|---------------------------------------------|----|

|    | 4.1  | Specifying compartments                     | 35 |

|    | 4.2  | Exposing library calls                      | 36 |

|    | 4.3  | Controlling interrupt state                 | 36 |

|    | 4.4  | Linking compartments                        | 37 |

| 5  | ABI  |                                             | 39 |

|    | 5.1  | Compartment layout                          | 39 |

|    | 5.2  | Access to globals                           | 39 |

|    | 5.3  | Export table layout                         | 41 |

|    | 5.4  | Import table layout                         | 42 |

|    | 5.5  | Cross-compartment calls                     | 43 |

|    | 5.6  | Cross-library calls                         | 43 |

|    | 5.7  | Callbacks                                   | 44 |

|    | 5.8  | Relocations                                 | 44 |

| 6  | Kno  | wn caveats                                  | 47 |

|    | 6.1  | Shared stacks                               | 47 |

|    | 6.2  | Explicit leakage                            | 48 |

|    | 6.3  | Availability                                | 49 |

| II | Ar   | chitecture specification                    | 51 |

| 7  | The  | CHERIOT ISA                                 | 53 |

|    | 7.1  | Starting subset of RV32                     | 53 |

|    | 7.2  | Omitted CHERI features                      | 53 |

|    | 7.3  | Changes to register file                    | 54 |

|    | 7.4  | Instruction encodings                       | 54 |

|    | 7.5  | Changes to instruction fetch / control flow | 54 |

|    | 7.6  | Changes to memory accesses                  | 55 |

|    | 7.7  | Tagged memory                               | 55 |

|    | 7.8  | Temporal safety                             | 56 |

|    | 7.9  | Controlling access to system registers      | 56 |

|    | 7.10 | Special capability registers                | 57 |

|    |      | Changes to exception handling               | 58 |

|    |      | The AUIPC and AUICGP instructions           | 59 |

|    |      | Capability encoding                         | 60 |

|    | ,.13 | 7.13.1 Capability permissions               | 60 |

|   |       | 7.13.2 Sealed capabilities                                        | 5 |

|---|-------|-------------------------------------------------------------------|---|

|   |       | 7.13.3 Capability bounds                                          | 7 |

|   |       | 7.13.4 Set bounds operation                                       | 9 |

|   |       | 7.13.5 Representability checks                                    | 0 |

|   |       | 7.13.6 The NULL capability                                        | 1 |

|   |       | 7.13.7 Zero length capabilities                                   | 1 |

|   |       | 7.13.8 Zero permission capabilities                               | 2 |

|   |       | 7.13.9 Capability layout in memory                                | 2 |

|   |       | 7.13.10 Sail implementation                                       | 2 |

|   | 7.14  | Instruction compression                                           | 2 |

|   |       | Stack high water mark                                             | 3 |

| 8 | Instr | ruction encoding summary 7                                        | 5 |

|   | 8.1   | Primary new instructions                                          | 5 |

|   |       | 8.1.1 Capability-Inspection Instructions                          | 5 |

|   |       | 8.1.2 Capability-Modification Instructions                        | 6 |

|   |       | 8.1.3 Pointer-Arithmetic Instructions                             | 6 |

|   |       | 8.1.4 Pointer-Comparison Instructions                             | 6 |

|   |       | 8.1.5 Special Capabilty Register Access Instructions              | 6 |

|   |       | 8.1.6 Adjusting to Compressed Capability Precision Instructions 7 | 7 |

|   | 8.2   | Modifications to existing RISC-V instructions                     | 7 |

|   |       | 8.2.1 Control-Flow Instructions                                   | 7 |

|   |       | 8.2.2 Memory-Access Instructions                                  | 7 |

|   |       | 8.2.3 Address Construction Instructions                           | 7 |

|   | 8.3   | Encoding Summary                                                  | 8 |

| 9 | Instr | ruction reference 8                                               | 3 |

|   | 9.1   | Sail language used in instruction descriptions                    | 3 |

|   | 9.2   | Constant Definitions                                              | 5 |

|   | 9.3   | Function Definitions                                              | 5 |

|   | 9.4   | CHERIOT Instructions                                              | 8 |

|   |       | AUICGP                                                            | 9 |

|   |       | <b>AUIPCC</b>                                                     | 0 |

|   |       | <b>CAndPerm</b>                                                   | 1 |

|   |       | CClearTag                                                         | 2 |

|   |       | CGetAddr                                                          | 3 |

|   |       | <b>CGetBase</b>                                                   | 4 |

|   |       | CGetHigh 9                                                        | 5 |

|   | CGetLen                                                     | 96  |

|---|-------------------------------------------------------------|-----|

|   | CGetPerm                                                    | 97  |

|   | CGetTag                                                     | 98  |

|   | CGetTop                                                     | 99  |

|   | CGetType                                                    | 100 |

|   | CIncAddr                                                    | 101 |

|   | CIncAddrImm                                                 | 102 |

|   | CJAL                                                        | 103 |

|   | CJALR                                                       | 104 |

|   | CLC                                                         | 106 |

|   | CMove                                                       | 109 |

|   | CRepresentableAlignmentMask                                 | 110 |

|   | CRoundRepresentableLength                                   | 111 |

|   | CSC                                                         | 112 |

|   | CSeal                                                       | 114 |

|   | CSetAddr                                                    | 116 |

|   | CSetBounds                                                  | 117 |

|   | CSetBoundsExact                                             | 118 |

|   | CSetBoundsImm                                               | 119 |

|   | CSetEqualExact                                              | 120 |

|   | CSetHigh                                                    | 121 |

|   | CSpecialRW                                                  | 122 |

|   | CSub                                                        | 124 |

|   | CTestSubset                                                 | 125 |

|   | CUnseal                                                     | 126 |

| П | I Appendices 1                                              | 127 |

| A | Version history                                             | 129 |

| В | Sail listings for capability encoding                       | 131 |

|   | B.1 SMT validation of properties of the capability encoding | 137 |

| C | Permission compression rationale                            | 141 |

| D | Potential revised bound encoding                            | 143 |

| $\mathbf{E}$ | Prop             | posed compressed instruction encoding changes                    | 145 |

|--------------|------------------|------------------------------------------------------------------|-----|

|              | E.1              | Compressed CMove and CIncAddr                                    | 145 |

|              | E.2              | Three-operand compressed instructions                            | 146 |

| F            | Stan             | ding on the Shoulders of Giants                                  | 147 |

|              | F.1              | CTSRD CHERI, CHERI-RISC-V, Morello, and CheriBSD                 | 147 |

|              |                  | F.1.1 Translation vs. Protection                                 | 147 |

|              | F.2              | Incorporated CHERI Extensions                                    | 148 |

|              |                  | F.2.1 Multi-Root, Compressed Permission Encodings                | 148 |

|              |                  | F.2.2 Recursive Permissions                                      | 148 |

|              |                  | F.2.3 Architectural Seals                                        | 149 |

|              |                  | F.2.4 Capability Load Barrriers and Memory-Capability Versioning | 149 |

|              | F.3              | Esswood's CheriOS                                                | 149 |

|              | F.4              | Xia's CheriRTOS                                                  | 150 |

|              | F.5              | Almatary's CompartOS and CheriFreeRTOS                           |     |

| Bil          | Bibliography 153 |                                                                  |     |

# Part I Software model and toolchain

# **Chapter 1**

## Introduction

The CHERIOT (Capability Hardware Extension to RISC-V for Internet of Things, pronounced like 'chariot') design is heavily based on prior work by the CHERI project. Our RISC-V extension is based on the CHERI ISAv8[22] and would not have been possible without this work.

This document describes the current status of the CHERIoT ISA. This ISA is not intended to be a final CHERI specification for embedded RISC-V devices but is a work-in-progress that is sufficiently close to final that feedback is valuable. In particular, the current C extension to RISC-V makes a number of optimization decisions that are not useful in a CHERI context and so we would likely benefit from an alternative (as yet unspecified) 16-bit instruction extension for embedded CHERI targets.

The CHERIoT project would not have been possible without the existing "big CHERI" research [6, 22], exploration of green-field CHERI-aware operating systems [8], and work to adapt CHERI software models to embedded systems [1, 2, 24, 25]. This ISA attempts to scale CHERI down yet further, into smaller embedded systems than previously considered; we have taken the opportunity to simultaneously design our ISA, compartment model, programmer model, compiler, and RTOS [16]. The capability encoding and instruction set have been tuned to enable this use and validated by running existing embedded software in compartments. Curious readers are invited to see our study of related works in Appendix F.

This document describes:

- The RISC-V ISA extension (Part II).

- The compartment model that the ISA is intended to support (Chapter 2).

- The RTOS implementation used to enforce the model (Chapter 3)

- The language extensions used to expose this model to developers (Chapter 4).

- The ABI used to implement the compartment model (Chapter 5).

Performance, power, and area costs for the implementation are not part of this and will be presented in a follow-up publication.

#### 1.1 The CHERIOT RTOS Model

Because the ISA given here is the result of simultaneous design with software, we will often refer to software concepts for motivation or justification of design choices. Particularly central to the discussion are the notions of memory safety, compartments, and threads. We provide coarse definitions here and will refine them as we continue.

A **thread** is a schedulable entity associated with a general-purpose register file and a designated region of memory for use as a call stack. Threads are either running, in which case their register file is the CPU's, or suspended, in which case the register file is saved to memory for later use.

A system is said to be **memory safe** if its references to memory are:

**Unforgeable** A reference to memory (in particular, the authority to access memory) can be constructed only from other references.

**Monotonic** A constructed reference will have no more authority than its progenitor reference(s) (and may have less).

**Spatially Safe** References to memory authorize access to a set of memory locations determined when the reference is constructed.

**Temporally Safe** References to a region of memory will not remain usable across *reuse* of memory for a different allocation.

CHERIOT is based on CHERI and so language-level references are expected to compile down to CHERI capabilities. We may gloss over subtle distinctions and conflate the terms "capability," "pointer," and "reference."

A **compartment** is a collection of code, data, and capabilities that serves as an invocable security context. Compartments statically export *entry-points*, which may be statically imported by other compartments or passed as opaque *cross-compartment function point-ers*. A compartment that (statically or dynamically) imports an entry point may then invoke it to perform a *cross-compartment call*. Such calls are synchronous and transition the calling thread from one compartment to another. The thread's stack is used, with appropriate bounds adjustment, in both the caller and callee compartment.

17

#### 1.2 Security goals

We aim to provide a minimal TCB that can run user software (including third-party code) in compartments. These compartments are not part of the TCB and are assumed to have a mutual distrust relationship with each other.

We define a set of security guarantees that apply to all untrusted compartments. These guarantees are enforced by three system components, which form the TCB for confidentiality and integrity. These components are:

**The loader,** which is responsible for setting up all of the initial capabilities for everything in the system. This never accesses any data that was not part of the initial firmware image.

**The switcher,** which is responsible for transitions between compartments and between threads. This is around 300 instructions in hand-written assembly.

**The memory allocator,** which is responsible for providing the hardware with the information required to enforce heap memory safety.

The code in these components must be carefully audited.

An embedded system may have user-provided components that run at the highest priority level, with interrupts disabled. Any code that runs with interrupts disabled is part of the TCB for availability.

#### 1.2.1 Heap memory safety

CHERIOT RTOS provides a **heap**, a system-provided compartment with dedicated memory to which it grants other compartments dynamic, temporary access.

The allocator ensures that the capabilities it gives out have bounds that do not overlap any other allocation, and so the CHERI bounds checks enforce spatial memory safety. Heap memory is also temporally safe: no heap memory will be reused until the system has ensured that all dangling pointers to it are deallocated. The hardware provides a guarantee that no capability can be loaded if the memory allocator has marked the memory it points to as deallocated. This mechanism is described in detail in Section 7.8. A revocation service (which can be implemented in hardware or software) periodically scans all memory and deletes capabilities that point to revoked memory.

The memory allocator is part of the TCB as it could violate confidentiality and integrity in a number of ways. It holds a capability to the entire heap and so, in principle, can violate confidentiality of heap contents either directly or by failing to clear memory before issuing an allocation in reused space. Similarly, it can violate integrity by directly using or improperly revealing capabilities held within heap memory. It can violate spatial safety by

not correctly bounding capabilities it returns. Finally, it could violate temporal safety by either not marking freed objects as deallocated or by un-marking the memory and reusing it before revocation.

However, despite all that, the memory allocator does not hold capabilities to normal compartment memory, only to region(s) reserved for the heap it manages. As such, even a completely compromised memory allocator can violate safety properties of the heap only; it cannot directly violate memory safety for non-heap memory.

#### 1.2.2 Local stack memory safety

Allocations on a thread's stack are bounded by CHERI capabilities – the compiler generates instructions to derive these capabilities from the stack capability – but are not guaranteed to be temporally safe.

However, CHERIOT ISA and CHERIOT RTOS have mechanisms to ensure that capabilities to stack allocations can not be stored anywhere other than on the stack to which they point (which may include address-taken allocations on the caller's portion of the stack). In practice, this means that violating stack temporal safety is very difficult: stack-derived capabilities cannot be stored onto the heap or into a global (it will deliver a trap). Therefore, the only way of having a stack pointer outlive the allocation is to store it through another stack-derived pointer that points to a higher frame or return it directly in a register.

#### 1.2.3 Cross-compartment stack memory safety

During a cross-compartment call, the thread and its stack transition security contexts. The stack bounds are restricted so that the callee has no access to the caller's stack, except via capabilities that are explicitly passed as arguments. This suffix of stack memory accessible to the callee is zeroed both on call and on return, which prevents any information leak from uninitialized memory. The implicit stack pointer and stack-derived arguments provided by the caller are the only pointers that are both held by a compartment and capable of storing other stack-derived pointers.

#### **Lexically-Scoped Delegation**

CHERIOT ISA's capability permission scheme allows software to derive variants of capabilities that can be stored only to stack memory. Additionally, CHERIOT ISA can impose this derivation *transitively* per capability: any capability loaded via such a capability becomes another such and, so, will impose the same on those loaded through it, and so on.

19

These two mechanisms allow for **lexically-scoped delegation**: a calling compartment may, for any capability it holds, construct a variant that can only be stored to the stack and can load only capabilities that can be stored only to the stack. Passing this derived capability to the callee ensures that the callee compartment cannot capture either the passed capability or any loaded through it in memory not visible to (and mutable by) the caller after return.

#### **1.2.4** Global memory safety

All objects with static storage duration are compartment-local and are visible to any thread executing within a compartment. Memory safety for globals is therefore advisory (untrusted code can simply access the global capability directly). The compiler will insert bound for any address-taken global. Immutable objects with static storage duration are derived from **PCC** (with the execute permission removed) and so cannot be written to.

#### 1.2.5 Higher-level security properties

The local security properties outlined above are used to build isolation between threads and compartments. This leads to the following high-level security goals:

- No compartment should be able to access another compartment's data, except where explicitly shared.

- No thread should be able to access another thread's data, except where explicitly shared.

Compartments that have not been explicitly granted the rights to run with interrupts disabled should also not be able to impact availability.

#### 1.2.6 Threat model

We assume that code running in a compartment is untrusted. As such, an attacker is assumed to have the ability to execute arbitrary code within a compartment. It is not possible to prevent programmers from introducing bugs but we aim to provide a set of tools that will make it easy to write code in a compartment that is able to protect itself from another attacker-controlled compartment that can invoke its entry points.

# Chapter 2

# **Compartment model**

CHERI is designed to support fine-grained compartmentalization. A compartment, in the CHERI sense, is defined by the memory that is transitively reachable<sup>1</sup> from the capability registers in the running code. The mechanism for transitioning between compartments is key to any CHERI compartmentalization strategy.

The original CHERI/MIPS prototype had an instruction that raised a synchronous abort, providing a transition into an in-kernel compartment switcher. Morello and newer CHERI/RISC-V implementations for large systems have instructions that perform atomic unsealing and domain transition. This provides a rich set of tools for building compartmentalization models but leaves concerns such as stack management to the software stack. The CHERIOT model relies on a mixture of hardware and software to enforce compartment isolation.

The threat model for this work assumes that compartments all exist in a mutual distrust relationship with each other. Compartments should not be able to see or tamper with other compartments' data unless they are explicitly granted access to it via capabilities passed across an exposed interface.

Compartments, in isolation, are not automatically trusted (or untrusted) with respect to availability. Each compartment explicitly lists the entry points that it exposes or may invoke that run with interrupts disabled and it is the responsibility of the firmware integrator to determine whether this is acceptable. For a compartment to run code with interrupts disabled, the linker and loader must have explicitly granted it these rights when initializing capabilities, and so it is possible for the firmware integrator to audit the compartment graph.

This is intended to give flexibility for system integrators with different levels of realtime requirements. At one extreme, a hard-realtime control loop can run in a realtime-

<sup>&</sup>lt;sup>1</sup>i.e. including memory reachable from capabilities loadable from memory by any number of indirections

priority thread, with interrupts disabled except at explicit yield points. Other threads in such a system would not be allowed to call any compartment entry points that can invoke functions that run with interrupts disabled and so the realtime-priority thread can always resume in the context-switch time. A somewhat softer realtime system may allow a small number of functions to be invoked from compartments that are exposed to lower-priority threads. These functions would be audited to ensure that their worst-case execution time didn't cause realtime components to miss their guarantees. At the weakest extreme, global forward progress is purely a best-effort objective and any compartment may be allowed to call functions that have no guarantees on bounded execution time and run with interrupts disabled.

We expect that compartments may be provided by untrusted third parties and so it is important that every cross-compartment interaction is amenable to auditing. In particular, the linker can see everything that the loader will set up and the loader is required to explicitly grant access to a compartment for every:

- MMIO region that a compartment has access to.

- Cross-compartment entry point that a compartment exposes (and its interrupt status on entry).

- Internal function that a compartment may run with interrupts disabled.

- Cross-compartment call that a compartment may perform to another compartment.

- Shared library routine that a compartment may invoke.

This is sufficient to retrieve a complete graph of cross-compartment communication, including which compartments may be running with interrupts disabled. This provides tools for firmware integrators to write policies such as:

- Only the specific code that the regulator approved may communicate directly with this device.

- Any code may run on the device but only the TLS compartment may talk to the network stack and only a compartment that exposes a small set of well-defined APIs may call the TLS stack.

- There must be no interaction between any of the compartments managing service

A and the compartments managing service B on the device, except yielding via the

scheduler.

#### 2.1 Compartments define spatial ownership

At its most reductionist, a CHERIOT RTOS compartment is defined by two registers:

**PCC** is the program-counter capability, which is used to reach code and read-only globals. **CGP** is the capability global pointer, which is used to reach read-write globals.

These define a set of code and data that represents a compartment. A compartment is a single security context. While running in a compartment, any code in the memory reachable by **PCC** may be executed, any data in that memory may be read, and any data in the globals reachable from **CGP** may be read or written.

Note, in particular, that compartments are responsible for enforcing an object abstraction on top of their global memory. The C/C++ compiler will automatically insert bounds when the address of a global is taken but an assembly programmer in a compartment is able to reach any globals. Our security model assumes that all code within a compartment trusts all other code within that compartment.

#### 2.2 Threads define temporal ownership

A CHERIOT RTOS thread is a schedulable entity that owns a stack, a trusted stack, and a register set. When a thread is scheduled, it owns the microcontroller's register file. When it is suspended, the register file is stored in a register save area.

Each thread is isolated from other threads. The CHERIOT ISA provides a simple 2-bit information-flow enforcement mechanism in the form of the global bit and the store-local permission. Capabilities without the global bit can be stored only via capabilities that have the store-local permission. In CHERIOT RTOS, only three types of memory have the store-local permission:

**Stacks**, reachable from a running thread's **CSP** and any capabilities derived from this (address-taken stack allocations).

**Register save areas**, reachable only from a special capability register (SCR) that are used to store a thread's state on context switch.

**Trusted stacks**, reachable only from a SCR, which are used to save and restore the stack pointer on compartment switch (more on this later).

Of these, normal compartment code has access only to the stack. The latter two are a single allocation that is reached via a SCR. The switcher is the only code that runs (after the loader has exited) with the rights to access this SCR. Threads' register files and stacks dynamically define a set of reachable objects.

# 2.3 Execution at the intersection of threads and compartments

Threads do not own code and compartments do not own a register file. Execution requires (at least) both of these and happens when a thread is scheduled to run within a specific compartment. Each thread starts at an entry point within a compartment and execution continues within that compartment until either the thread calls another compartment or a context switch invokes another thread.

This means that running code always has access to the code for the current compartment, the globals for the current compartment, the part of a thread's stack and register state associated with the current compartment invocation. Two threads might be in the same compartment at the same time (one of them preempted or yielded, the other running), if the compartment permits this. If two threads enter the same compartment (either at the same time or sequentially) then they will see the same set of globals and can use them to communicate.

Globals (more specifically, capabilities derived from the value in the **CGP** register) do not have store-local and so it is not possible to construct a capability that is reachable from a global and which points to a stack allocation. This gives strong cross-thread isolation. If a thread enters a compartment that is compromised, a thread running compromised code within that compartment cannot tamper with the victim thread's stack or register file and must use data-oriented attacks from data reachable from globals.

#### 2.4 Compartment switches enforce compartment isolation

Cross-compartment calls require that a thread loses access to one compartment and gains access to another. CHERI provides a *sealing* mechanism to build this kind of model. We use this with an explicit compartment switcher to build a robust compartment invocation mechanism for embedded systems.

When a thread wishes to invoke another compartment, it loads two capabilities from its import table (see Chapter 5). The first is a sealed capability to a structure describing the entry point in the callee. The second is a *sentry* capability to the compartment switcher. The sealed capability is passed in a register when the sentry capability is called.

A CHERI sentry is a capability that can be jumped to but cannot be used for any other operations. The CHERIOT ISA extends this by allowing different kinds of sentry to control interrupt state. The sentry for the compartment switcher implicitly disables interrupts on entry to the switcher, which makes it easier to reason about the execution flow within the switcher.

The compartment switch routine unseals the target capability and uses it to find the **PCC** and **CGP** of the target compartment, and the offset within the **PCC**. It can then construct a target to invoke. In addition, it reads the number of registers that the callee expects to have passed (which it uses to zero unused argument registers) and the interrupt status for the callee (which it uses to reenable interrupts immediately prior to invocation, if required). The RV32E ABI defines only two callee-save registers. The switcher saves these onto the trusted stack and then zeros all non-argument registers except for **CGP** and **CSP**, which have special handling.

In addition to these steps, the compartment switcher is responsible for preventing the stack from being used to leak data between compartments (other than via explicit arguments). This requires several steps. First, the stack passed in the **CSP** register must be shrunk to allow CHERI's spatial bounds protection to prevent any access by the callee to the caller's portion of the stack. Second, both before a call and before completing the return transition, the compartment switcher zeroes the portion of the stack that is made available to the callee. Zeroing the stack seems expensive but recall that in embedded systems a 2 KiB stack is considered *very* large. Our stacks are typically 1 KiB. With a 33-bit memory bus, we need 256 stores (in the worst case) to zero the whole thing. That's more expensive than a function call, but not vastly so. Additionally, the hardware provides a stack high water mark (see Section 7.15) to minimise the amount of zeroing required.

At the end of a compartment transition, the new compartment has access to:

- Its own code (**PCC**)

- Its own globals (CGP)

- A portion of the thread's stack, excluding any frames owned by the caller, and full of zeroes.

- Any memory pointed to by argument capability registers, passed explicitly from the caller.

On return, any temporary state is cleared and the caller has access only to explicit return capabilities.

This does not prevent one compartment from having access to another compartment's globals, but there are legitimate reasons for wanting this. For example, a compartment may derive a read-only (no store permission) capability to one of its globals and use that to cheaply broadcast state updates to subscribers.

#### 2.5 Context switches enforce thread isolation

Context switches happen as a result of an interrupt (including synchronous aborts / exceptions). The context switcher code saves the register file into a save area pointed to by a

SCR. The register save area and the trusted stack are both reached by the same SCR and the two switchers (thread and compartment) are the only code in the system that runs with permission to access this register after the loader has finished.

The context switch routine (part of the switcher's approximately 300 instructions) is the only code that is able to violate thread isolation. It has access to two threads simultaneously:

- The stack pointed to by **CSP** on entry to the interrupt handler.

- The stack that the scheduler will use, loaded from a read-only global in the switcher's **PCC**.

Before invoking the scheduler, the switcher will seal the capability to the register save area (from which the stashed **CSP** is reachable) and pass it as an argument into the scheduler. The scheduler is therefore in the TCB for availability but, crucially, not for confidentiality or integrity.

The scheduler runs with interrupts disabled and selects the next thread to run, returning a (sealed) capability to the register save area to the switcher. This must be sealed with the object type that the switcher expects. The loader guarantees that nothing except the switcher has a permit-seal capability for that type and so the scheduler is able only to provide register save areas that were previously provided by the loader or the switcher.

The current CHERIOT RTOS scheduler is a very simple priority scheduler that does round-robin scheduling within a priority level. A more complex one could be added for use cases that need something more complex without changing the security model. Conversely, an even simpler scheduler that exposes a less rich set of inter-thread communication primitives could be used for safety-critical systems.

The scheduler is a compartment just like any other and so can expose more complex scheduling operations such as message queues as cross-compartment calls that then explicitly yield.

#### 2.6 Adding shared libraries

In a compartmentalized system it is very common to have routines that are required from many different compartments. This is trivial to support by duplicating the code into all compartments that use it. On large systems with a memory-management unit it's possible to logically duplicate the code in the virtual address space without duplicating it in the physical address space. This is not possible on a system such as ours, without any virtual memory support.

27

Instead, CHERIOT RTOS provides a shared-library abstraction that is designed to work in concert with our compartmentalization model. A shared library is much like half of a compartment: it may contain code and read-only data (PCC) but may not contain read-write globals and so runs with the CGP of the caller. A function in a shared library runs with the context of the caller and so invoking a shared-library function does not need to go via the compartment switcher.

Cross-library calls, as with cross-compartment calls, must change **PCC** to a specific location in another block of code. This is enforced by the loader providing callers with a sentry capability to the jump target. This prevents the caller from being able to jump to arbitrary points in a shared library. It also allows shared libraries to expose routines that run with interrupts disabled. For example, on a core that doesn't provide native atomics, we can expose atomic-increment functions that perform a simple read-modify-write with interrupts disabled, without having to go via the compartment switcher.

# **Chapter 3**

# **RTOS** implementation

The CHERIOT RTOS is intended to provide a minimal TCB. The core of the RTOS comprises:

**A loader,** which runs before any untrusted data is encountered and sets up the capabilities for the rest of the system.

**Switch routines,** which add up to around 300 instructions in hand-written assembly, for switching between thread and compartments.

**A heap allocator,** which allocates memory from a shared heap for use by compartments. **A scheduler,** which selects the next thread to run.

Of these, only the loader and the switch routines run with access to the trusted stack and register save areas (that is, with the access-system-registers permission on their **PCC**). This means that these are the only two that can completely compromise all of the security properties on which the rest of the system is built. The loader runs once on system start and then erases itself. The loader is not needed on systems where the persistent storage (e.g. flash) can store tag bits.

The switch routines (currently) add up to a total of around 300 instructions, with no memory allocation and very little control flow. For comparison, the trusted (unverified) part of seL4 is 340 instructions [12], so CHERIOT RTOS contains less code in its TCB than seL4 contains unverified code in its TCB.

The heap allocator holds capabilities to the shared heap and the revocation bitmap for the shared heap and so is able to violate heap memory safety. The scheduler is more or less an untrusted compartment, though with a private stack. Importantly, the scheduler does not have access to the stacks, trusted stacks, or register-save areas of the threads that it manages. It may choose the next thread to run, but it cannot tamper with a thread's state.

#### 3.1 Per-thread state

Each thread has a stack (reachable from **CSP**) and a *trusted stack*. The trusted stack maintains the state required for cross-domain calls. The same data structure also contains the register save area, where the contents of the register file will be saved when an interrupt is delivered.

A capability to the trusted stack and register save area for the running stack is stored in the **MScratchC** register, which can be accessed only by code whose **PCC** has the permission to access system registers.

#### 3.2 The loader

The loader starts with access to the root capabilities and so has complete access to everything on start. The majority of the loader is written in C++ with rich types conveying intentionality, including templates that provide capability permission sets as compile-time constants that can be statically checked

The loader splits the architectural roots into four software-defined roots:

**Executable** capabilities are used for deriving capabilities that will end up installed in **PCC**.

**Global** capabilities do not have permit-store-local and are used for deriving capabilities for globals, heap memory, and so on.

**Local** capabilities do not have the global permission and are used only for stacks, trusted stacks, and register save areas.

**Sealing** capabilities have no memory-related permissions and are used only for sealing and unsealing.

Each capability that is derived from a root is derived via a mechanism that validates (at compile time) that the requested permissions are less than the permissions of the root.

The C++ portion of the loader is stored in a portion of memory that will eventually become the heap. Once it returns to a small assembly stub, this stub zeroes all of the memory used by the loader (stack, code, and globals) and almost all of the register file, ensuring that no capabilities are leaked. It then yields to the scheduler (via an ecall instruction) and becomes a stackless idle thread.

The loader is responsible for initializing import tables (the capabilities that may point outside of the compartment, see Chapter 5 for details), preparing each thread's initial state, and applying caprelocs (dynamically initialized capabilities stored in globals). For each capreloc, the loader finds the compartment that it refers to and attempts to derive the target

from the compartment's **PCC** and **CGP**. If this fails, then the boot image is corrupted and the loader resets (allowing a first-stage loader to perform A/B installations).

#### 3.3 Interrupt handling

The interrupt handling code is part of the switcher and runs with permission to access **MScratchC**. It first saves the register file in the current thread's register save area and seals the capability to this area. Next, it loads the other special-register values that describe the interrupt and prepares a context invoking the scheduler.

The scheduler is always invoked with the same stack, with arguments containing a sealed capability to the register-save area of the interrupted and yielding thread. It then returns a sealed capability to a register-save area for a thread to resume. The scheduler runs with interrupts disabled and provides a simple static priority scheduler with round-robin scheduling within a priority level. Threads are run when no thread with a higher priority is runnable. If two threads at the same priority level are runnable, one runs until it either yields or an interrupt is delivered, then the next one runs.

#### 3.4 Synchronization and scheduling primitives

The scheduler is a compartment and so can expose entry points that can be invoked via the switcher. These include semaphore and message queue interfaces that will park a thread (mark it as not runnable) until some event happens.

In addition, an MCall instruction will deliver an interrupt, causing the running thread to immediately yield. This is used for an explicit yield operation that transfers control immediately to the switcher and then to the scheduler. This mechanism can be used from inside the scheduler itself to allow a thread to yield after the scheduler has updated some data structures related to it.

In combination, these can be used to build synchronization primitives with timeouts. A thread that wishes to block waiting for an event calls the scheduler, which then records the conditions that will wake the thread (including the timeout) and yields via an MCall. One resume, the scheduler can check how long it slept for and return from the cross-compartment call.

#### 3.5 The memory allocator

The memory allocator currently provides a simple malloc-like API. Future versions will add explicit memory pinning (no concurrent deallocation of an object during a compartment invocation) and explicit permission to deallocate objects.

In addition, the allocator provides a mechanism for allocating sealable objects. The CHERIOT ISA has only a handful of sealing types and so it is not feasible for every compartment to be able to seal capabilities using the hardware mechanism. Instead, the memory allocator reserves one hardware sealing type for allocating sealable objects. A sealable object has a header describing the capability that is used to unseal it. The allocator will provide a sealed capability to the whole object (including the header) and, if invoked with the correct unsealing capability) will return an unsealed capability to all of the object *except* for the header.

This mechanism allows compartments to provide opaque data types to software running outside of the compartment.

#### 3.6 Error handling

One effect of the CHERI architecture is to turn errors that could result in memory corruption vulnerabilities into traps. To mitigate the availability concerns this could create, the CHERIOT RTOS provides a mechanism for recovering from faults in a controlled way. Compartments can define an error handler that will be called if a fault occurs during execution of that compartment, or if a fault in a called compartment results an 'unwind'. The error handler can inspect the saved register context from the time of the fault and can choose either to resume execution with an amended register context or to unwind the trusted stack, returning an error to the calling compartment.

Careful use of this mechanism can allow an application to continue even after it encounters an unexpected fault. For example, a compartment error handler might reset the compartment state before returning an error to the calling compartment. For more details of this mechanism and special security considerations please refer to the CHERIOT RTOS documentation.

#### 3.7 Other components

All other components, such as a network stack (taken from FreeRTOS), a TLS stack (from mBedTLS), and so on are untrusted. They are treated no differently from any other user-provided code and are packaged only for convenience. The bottom of the network stack

33

talks to a device driver, which is simply another compartment whose import table is used to grant access to the MMIO region containing the network device's control registers.

# **Chapter 4**

# C/C++ language and toolchain extensions

In addition to the existing CHERI C/C++ extensions, we define a small number of additional extensions that are specific to CHERIOT. CHERI C is already able to compile most existing embedded code that we have tried with no modifications. Embedded code has to tolerate targets with Harvard architectures, different pointer sizes for different types of data, different memory banks, and so on. In comparison, a CHERI target is far more like a conventional ISA.

We have not had to change the CHERI C model at all for code running within a compartment. Our extensions are focused on supporting the compartmentalization model.

#### 4.1 Specifying compartments

We have added an attribute to specify the compartment that implements a given function. This is used in conjunction with the -cheri-compartment= flag passed to the compiler, which specifies the compartment in which the current compilation unit will end up. The compiler will raise an error if the compartment name for the current compilation unit does not match the name of a function that has an implementation. For example, if a header file contains the following declarations:

```

1 __attribute__((cheri_compartment("example"))) void foo(int);

2 __attribute__((cheri_compartment("other"))) void bar(void);

```

If foo is implemented then the compiler must be invoked with -cheri-compartment=example. Any call to bar will then be treated as a cross-domain call.

This mechanism allows lightweight annotations on functions that are exposed across compilation units. Software that already supports a DLL-style linkage model may have macros on public functions for using this. Other software can easily maintain these annotations for CHERI targets with a macro that expands to nothing for non-CHERI targets.

Adding \_\_attribute\_\_((cheri\_ccallback)) to a function marks it as a cross-compartment callback. Taking the address of such a function will give a pointer that can be passed across compartments and allow the recipient to recursively invoke this compartment.

#### 4.2 Exposing library calls

Adding \_\_attribute\_\_((cheri\_libcall)) to a function marks it as a library call. The compiler will always generate an indirect call (via a sealing capability from the import table) for all library functions, unless the callee and caller are in the same compilation unit and have compatible interrupt states.

All of the functions that the compiler may insert calls to (such as memcpy, '\_\_cxa\_guard\_acquire , and so on) are assumed to implicitly carry this attribute. The compiler must be able to insert calls to these without knowing the name of the library that provides them and so this attribute provides a single flat namespace for all such functions.

#### 4.3 Controlling interrupt state

The cheri\_interrupt\_state attribute controls whether, during execution of the function, interrupts are enabled, disabled, or in whatever state there were for the caller. It takes a single argument, which must be either enabled, disabled, or inherited. The attribute can also be written as a C+11 / C2x-style attribute. For example:

```

// This function runs with interrupts disabled

[[cheri::interrupt_state(disabled)]]

int disabled(void);

// This function runs with interrupts enabled

-_attribute__((cheri_interrupt_state(enabled)))

int enabled(void);

// This function runs with whatever interrupt state the caller has.

-_attribute__((cheri_interrupt_state(inherit)))

int inherit(void);

```

All functions that are not exposed across compartment boundaries (including library calls) default to inherit. Cross-compartment calls default to enabled and must be set to either enabled or disabled.

37

# 4.4 Linking compartments

The version of LLD used with CHERIOT provides a -compartment flag for linking compartments. This is somewhat similar to -r, which creates a relocatable object file. Linking in this mode marks all symbols except for those in the export table as local. Unlike -r, COMDATs are merged when linking a compartment. In other respects, this is identical to -r: relocations are not processed and will be handled in the final link step.

# Chapter 5

# **ABI**

CHERIOT is a hardware-software co-design project, where the ISA and ABI have been carefully designed together to provide the desired compartment model and security guarantees.

# 5.1 Compartment layout

Each compartment has two reachable regions, bounded by **PCC** and **CGP**. The **PCC** region contains the compartment's code, read-only data, and *import table*. Read-only data includes relocation read-only data, which is initialized by the loader at boot time. A compartment's import table is a read-only table containing capabilities that are used for cross-compartment and cross-library calls, as well as any imported data.

A compartment also has an export table associated with it. The export table defines the set of functions that are exported from the compartment (callable by others). This is read by the compartment switcher (see Section 5.5).

Shared libraries are identical to compartments in structure, except that they lack a **CGP**.

# 5.2 Access to globals

Read-only globals are accessed using PCC-relative addressing. CHERI RISC-V extends the RISC-V auipc (add upper immediate to program counter) instruction to auipcc (add upper immediate to program counter *capability*). This adds a 20-bit immediate, left shifted by 12, to the current **PCC** value, giving an address that is within the immediate range of a RISC-V load or store instruction of the target.

40 CHAPTER 5. ABI

Unfortunately, the result of the auipcc instruction may be out of the bounds of **PCC**. This does not matter on CHERI systems with 128-bit capabilities because the encoding guarantees that capabilities remain valid 4096 bytes out of bounds. However, this is not the case with our 64-bit capability encoding that has much tighter 'representable bounds'. The tag bit is cleared if the capability is too far out of bounds, we must therefore modify the standard CHERI-RISC-V relocation scheme to avoid taking capabilities out of bounds in the middle of computing an address.

We are able to solve this problem by having at least a 1-bit overlap between the immediate field of the loads and stores (or cincoffset instructions) and the aupicc. The auipcc instruction and the second instruction must both displace the **PCC** in the same direction, keeping the intermediate capability in bounds and hence representable. If the target address is after the current instruction then both values must be positive, otherwise both values must be negative, which is a simple property for the linker to ensure when applying the relocations. To make this possible we reduce the shift of auipcc by one, meaning auipcc can always produce a value within the 2 KiB range required. This does limit the maximum offset for a relocation to less than  $2^{31}$  but this is not a problem in practice due to the limited size of compartments. Any system that needs more than 2 GiB compartments would likely benefit from a 64-bit address space.

Accesses to read-write globals is very similar. The **CGP** register is biased by half the size of the combined globals section (.data, .bss, and so on). This means that the full immediate range is accessible for displacements. With a 12-bit immediate, a single compartment can access 4 KiB of globals in a single load or store (or take their address with a cincoffset instruction). We define a new instruction, auicgp, and a relocation type that uses it to mirror the **PCC**-relative addressing mode.

We rely on linker relaxation to optimize both **PCC** relative and **CGP** relative relocations. This means that relocations within  $\pm 2$  KiB of **PC** or **CGP** require only one instruction. Given the security incentive to keep compartments small we expect relaxation to work well in the common case. In particular, if a compartment has more than 4 KiB of mutable global state it may be advisable to split it into multiple compartments or use dynamic allocation.

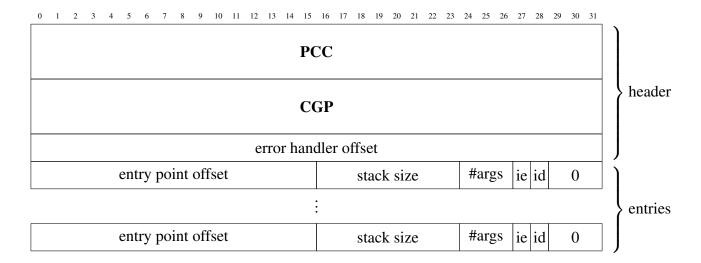

Figure 5.1: Compartment export table layout

# 5.3 Export table layout

Figure 5.1 shows the layout of the export table for a compartment. Each export table starts with a copy of the **PCC** and **CGP** for the target compartment. The next 32-bits is the offset of the compartment's error handler relative to **PCC.base**, or -1 if the compartment does not have an error handler. If an error occurs the switcher may jump to this as described in Section 3.6. After the header, the export table is comprised of one 32-bit entry per exported function. The first 16 bits of each entry provide the displacement from the start of the compartment's **PCC** to the entry point. This limits a compartment to exporting functions in the first 64 KiB of its code section. Most compartments have significantly under 64 KiB of code, the few that are larger can sort their internal layout to ensure that the exported functions all fit within the start.

The next 8 bits are the minimum amount of stack space that the function requires. This allows compartments to be defensive against callers that try to invoke them without enough stack space for their prologues. If a function requires more than 256 bytes of stack space then it can add a dynamic check on the size of **CSP** after the compartment switch.

The final 8 bits are reserved for flags, described in the following table:

<sup>&</sup>lt;sup>1</sup>An alternative solution would be to increase the size of the immediate on loads and stores. On RV32E this could be achieved using the register selection bits that are freed by moving from 32 to 16 registers. Our first prototypes did this but we choose to remain compatible with RV32I by modifying auipcc.

42 CHAPTER 5. ABI

| Bits | Meaning                            |

|------|------------------------------------|

| 0-2  | Number of argument registers used. |

|      | Interrupts enabled                 |

| 4    | Interrupts disabled                |

The compartment switcher is responsible for clearing all registers except for the used argument registers and so must know how many are used. The compiler fills in this set. This provides a value from 0 (no arguments) to 7 (all six argument registers used, plus **C5** carrying stack arguments.

Exports from compartments must set either the interrupts-enabled or interrupts-disabled bit. Code running in a different security context always runs with an explicit interrupt status, to make it easier to reason about compartment behavior. Functions exposed from shared libraries may set neither, in which case the function will be invoked with the caller's interrupt status.

Each export table entry from a compartment is exposed as a symbol of the form \_\_export\_{compartment name}\_{function name}. Each export table entry from a library is exposed as a symbol of the form \_\_library\_export\_{library name}\_{function name}. Libraries all use the same name in their export symbols because moving a function from one library to another does not involve running the target in a different security context. The existence of multiple libraries is purely to improve auditing: libraries (their entry points, called functions, and the contents of their code sections) can be individually tracked, allowing code-signing rules to be driven by specific implementations of individual libraries. For example, code signing might require a specific FIPS-certified binary of a crypto library, but allow the shared library providing memcpy to be replaced with a more optimised version.

The function name in the export symbol is mangled according to the Itanium C++ ABI rules. This provides some defense against accidental (non-malicious) type mismatches in the caller and callee.

#### 5.4 Import table layout

The import table is similar to a captable in structure. It is the only piece of state reachable from a compartment that is allowed to contain capabilities that point outside of the compartment's **PCC** and **CGP** on system start. This makes it a single place to audit the compartment graph. The import table is mutable only by the loader. After the loader finishes it is reachable only by the read-execute **PCC** for the compartment, not by any capabilities with store permission. Import table entries, at run time, are one of three things:

• Sealed capabilities to export table entries, used for cross-compartment calls.

- Sentry capabilities to library functions.

- Capabilities to memory-mapped I/O (MMIO) regions.

The loader is responsible for initializing these, based on information provided by the compiler and linker. Prior to the loader running, import table entries for the first two categories contain addresses of the corresponding export table entry. Import table entries for MMIO regions contain the start address and the size of the region. This allows a compartment to be granted a subset of an MMIO region, down to access to a single byte (for example, allowing a compartment to poll the 'ready' status of a UART but requiring that it performs a call to the compartment that owns the UART to read or write data with it). A future version will allow read- or write-only access to MMIO regions.

The loader will populate the import table with capabilities. Each import table entry that is used for cross-compartment calls will contain a sealed capability that has the bounds of the target compartment's export table and whose address points to the correct entry. This allows the switcher to load the **PCC** and **CGP** values from the start and to jump to the correct address.

The first entry in the import table has the (local) symbol name .compartment\_switcher. It is initialized to 0 at static link time and will be initialized by the loader with a sentry capability for jumping to the compartment switcher.

# 5.5 Cross-compartment calls

Cross-compartment calls pass their arguments in the same registers as the RV32E ABI (C10–C15). In addition, any stack arguments are passed via C5 (Ct0). The callee does not have access to the caller's stack other than via these arguments and so cannot use CSP-relative addressing for on-stack arguments.

The capability loaded from the import table is passed to the switcher in C6 (Ct1). The last step on the caller side is to jump to the sentry pointed to by the .compartment\_switcher symbol.

If a compartment calls a function that it also exports, and that function has the same interrupt status as the caller, then the compiler may insert a direct call and skip the switcher.

#### 5.6 Cross-library calls

Cross-library calls are simple indirect calls via a capability provided in the import table. The import table entry contains a sentry capability to the target function. The CHERIOT

44 CHAPTER 5. ABI

ISA has sentries that enable, disable, or inherit the current interrupt status and so crosslibrary calls can toggle or preserve the interrupt state. This makes it easy to reason about the current interrupt state using structured programming idioms.

If a function explicitly changes interrupt state within a compartment then it will be handled as if it were a library function exported from and consumed by the function. In this case, the symbol in the export table will be local.

#### 5.7 Callbacks

In some situations, one compartment wishes to provide a callback that another compartment can invoke. In the CHERIOT ABI, this callback is represented as the same form of sealed capability that would be loaded from the import table. Functions used as cross-compartment callbacks are both exported and imported by the compartment that wishes to take their address. Taking the address of such a function is simply a load from the import table.

As with non-exported functions that change the interrupt status, the symbol in the export table will be local if the function is not also exported as a directly callable function.

#### 5.8 Relocations

The relocations added to RISC-V for CHERIOT ABI are listed in Table 5.1. As with existing RISC-V, some of these are in two forms because RISC-V loads and stores place their immediate operands in different locations. The relocation numbers here are the ones used in the current prototype and are expected to change prior to standardization.

**PCC** or **CGP** relative relocations consist of a pair of either auipcc or auicgp plus a 12-bit immediate instruction. In most cases (when the offset is within  $\pm 2$  KiB) linker relaxation can reduce this to a single instruction for **CGP**-relative accesses. The AUICGP instruction uses an entire major opcode and is rarely needed because it is uncommon for a compartment to have more than 4 KiB of read-write global data (arguably a large globals section is an indication that a compartment should be split or refactored). Therefore, in future we could consider alternative relocations that don't require auicgp, such as a three instruction sequence consisting of lui, addi and cincaddr. This would require more complex linker relaxations to retain good code size and efficiency and we have not yet attempted it.

The same relocations are applied for both **PCC** and **CGP** relative accesses. The linker is responsible for determining the target of the relocation and will rewrite auipcc or auicgp

5.8. RELOCATIONS 45

| Relocation               | Value | Meaning                                               |

|--------------------------|-------|-------------------------------------------------------|

| CHERIOT_COMPARTMENT_HI   | 220   | 20-bit, 11-bit shifted PCC- or CGP-                   |

|                          |       | relative displacement for use in auicgp or            |

|                          |       | auipcc.                                               |

| CHERIOT_COMPARTMENT_LO_I | 221   | 12-bit <b>PCC</b> - or <b>CGP</b> -relative displace- |

|                          |       | ment for use in I-type instructions.                  |

| CHERIOT_COMPARTMENT_LO_S | 222   | 12-bit <b>PCC</b> - or <b>CGP</b> -relative displace- |

|                          |       | ment for use in S-type instructions.                  |

| CHERIOT_COMPARTMENT_SIZE | 223   | The size of the referenced symbol, ap-                |

|                          |       | plied to a CSetBounds instruction.                    |

Table 5.1: The relocations defined for the CHERIOT ABI

to the correct instruction depending on the target and update the offset depending on the kind of target.

# Chapter 6

# **Known caveats**

There are a small number of known caveats for developers attempting to secure a compartment. Future iterations may have compiler mitigations for some of these.

#### 6.1 Shared stacks

Compartments invoked by the same thread all use the same stack. This is important for embedded systems. Embedded stacks are often on the order of 1 KiB in size and so requiring a separate stack segment for every thread and compartment pair would quickly exhaust memory. This sharing provides one useful tool for an attacker: The caller has access to all of the callee's stack prior to a call.

A malicious compartment may construct a capability to a currently-unused part of the stack, which will become the callee's stack. It cannot stash these on the heap or in globals but it can then pass these as arguments. The compartment switcher will check that these are not passed as direct arguments but a compartment may load a capability and corrupt its own state. For example, consider the following interface:

```

struct A

{

char *outBuffer;

size_t length;

};

-_attribute__((cheri_compartment("victim")))

void copyOutSomething(const struct A *out);

```

This API takes a structure containing a pointer to a buffer and a length and is expected to write something via this pointer. If the attacker sets up the outBuffer field to point to

something on the victim's stack, then the victim may corrupt its own stack. The victim must check this. The check\_pointer function from cheri.hh validates that pointers do not do this. This function takes a set of permissions that the capability must have and a size (optionally: if unspecified it assumes that the pointer must be big enough for one instance of pointee type) and returns true only if the pointer is not on the current compartment's stack, is tagged, unsealed, and has sufficient permissions.

The following snippet is taken from the implementation of one of the scheduler functions.

This ensures that the **void** \*\*ret argument can be used to store a capability. If this is not the case, the function returns early.

# **6.2** Explicit leakage

Passing a pointer to a cross-compartment function call at the C level grants the callee access to the pointee data. Similarly, returning a pointer from a cross-compartment function call grants the caller access to the pointee. The ISA provides several tools for restricting this: